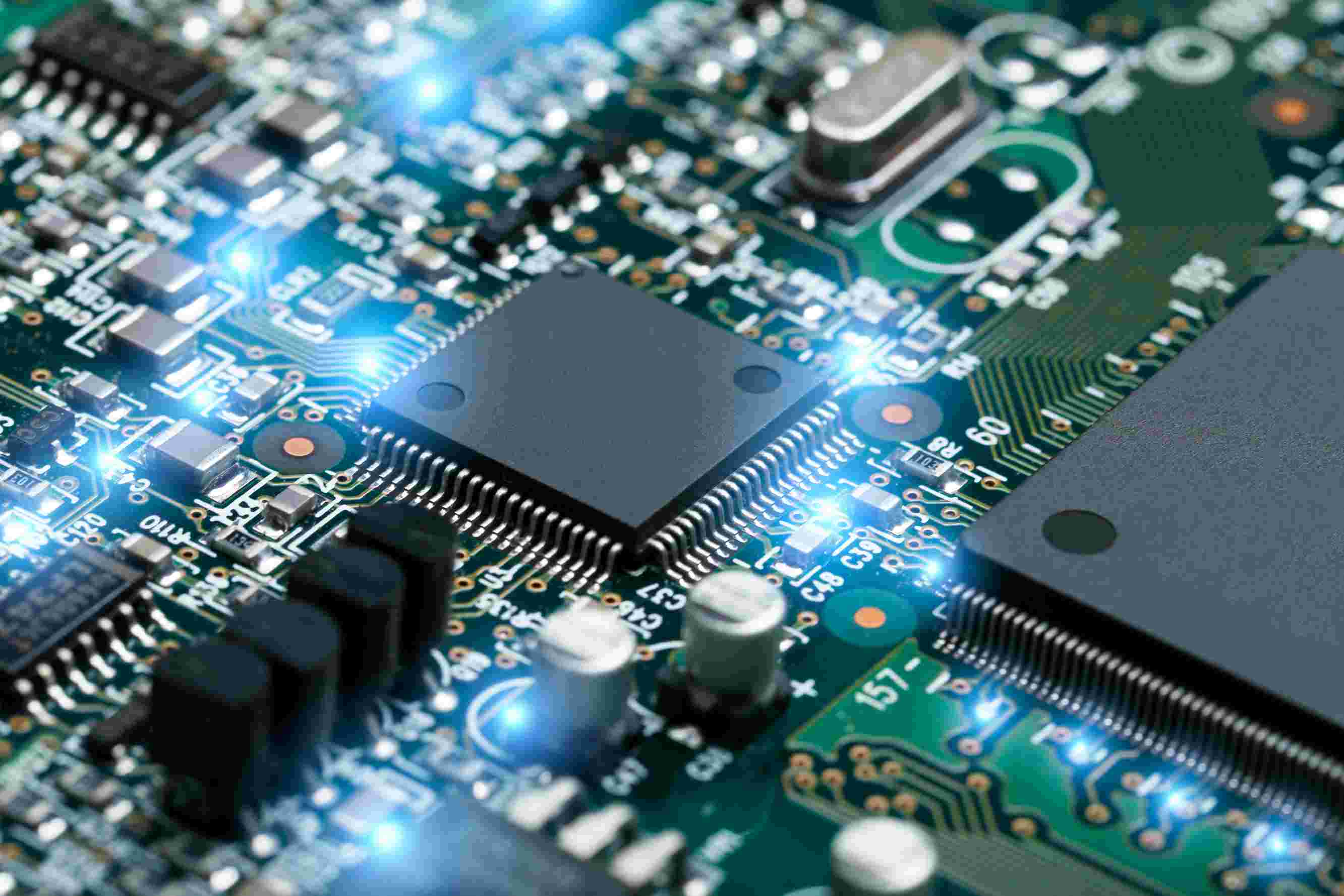

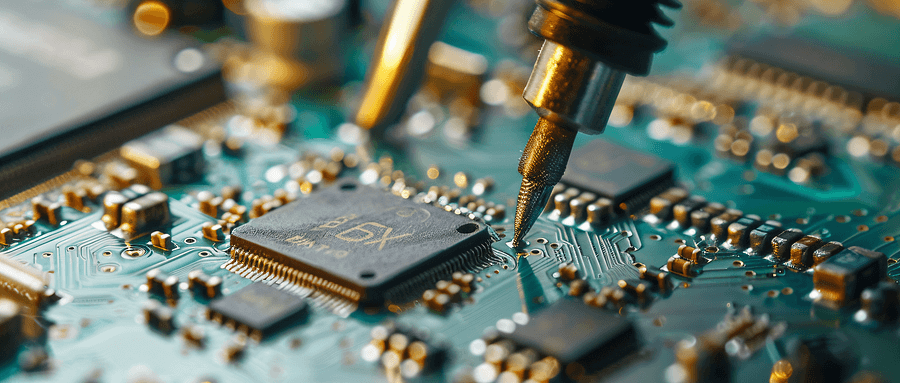

Latch-up refers to a phenomenon where instantaneous current becomes locked or amplified, resulting in a short circuit between the chip’s power supply and ground, which can damage the chip due to the excessive current.

| Project Overview

Latch-up refers to a phenomenon where instantaneous current becomes locked or amplified, resulting in a short circuit between the chip’s power supply and ground, which can damage the chip due to the excessive current. As the integration density of semiconductor circuit design continues to increase, instantaneous variations in voltage or current have become increasingly damaging to chips. In addition, some sectors of the semiconductor industry believe that the frequently occurring issue of Electrical Over Stress (EOS) in returned products is closely related to latch-up testing, which makes this type of testing critically important.

| Testing Standards

Latch-up testing primarily follows the JEDEC 78 standard and the AEC-Q100-004 definition. In automotive electronics testing, the requirement specifies the use of Class II, meaning the maximum operating temperature condition, which is significantly stricter than traditional room-temperature testing.

| MTT Advantages

MTT provides a complete suite of semiconductor chip reliability test programs, supporting clients in achieving compliance with international reliability standards such as JEDEC, MIL-STD, and AEC-Q.

1. Professional Team: A team of highly experienced testing engineers and technical experts.

2. Advanced Equipment: Equipped with internationally leading testing instruments to ensure accuracy and reliability of results.

3. Efficient Service: Rapidly respond to customer needs and provide one-stop, high-efficiency inspection services.

4. Authoritative Certification: The laboratory is certified by ISO/IEC 17025, ensuring that test reports have international credibility.